RESEARCH & DEVELOPMENT (R&D)

Silicon Interfaces® teams have undertaken Research and Development in diverse areas. like Power Verification™ - UPVM© - Low Power Class-based Library, Scaling down Fault Simulation cycle time using Artificial Intelligence and Machine Learning modeling techniques, PCIe Race Condition resolution with Data Integrity/Security using Memory Manager and Fabric Matrix. These research areas have been undertaken by Silicon Interfaces Research Engineers to solve specific problems in domains of early stage Low Power Verification, application AI/ML to Fault Simulation, Data Integrity/Security as well multi-Core ALU enhcancements using Vedic Multipliers. The Research findings have been presented in several Conferences in North America, Europe, and Asia Pacific:

PCIe Race Condition resolution with Data Integrity/Security using Memory Manager and Fabric Matrix

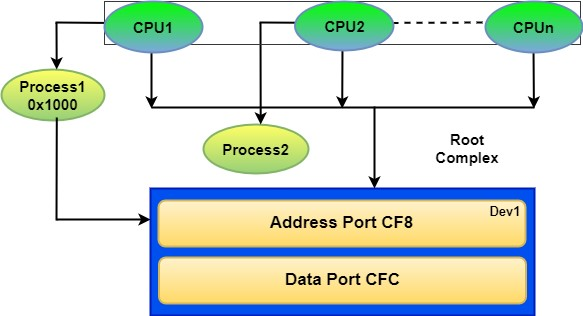

- From the start PCIe Interconnect has been susceptible to a Race Condition and also Data Integrity/Security issues especially in a multi-Core environment operating as single CPU or as in Clusters. The port CF8 and CFC has been allocated for Address and Data transmission. The CPU or any Core retrieves the BDF from Configuration Space Registers for the End Point Device information and writes to CF8 and once the Depth First Search Algorithm has identified the End Point, the Data is sent thru CFC Port. In a multi-Core environment, the Bus0 has many sources and leading to Race Condition and Data Integrity issues.

- Silicon Interfaces has a solution using Portable Stimulus and Test Standard (PSS) using the Parameterization, Resource Share and Lock to ensure that the Data goes to the right End Point as well as Memory Management.

Introduction

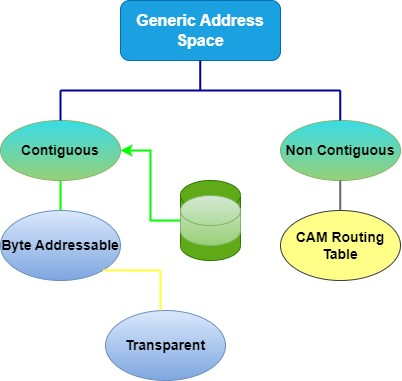

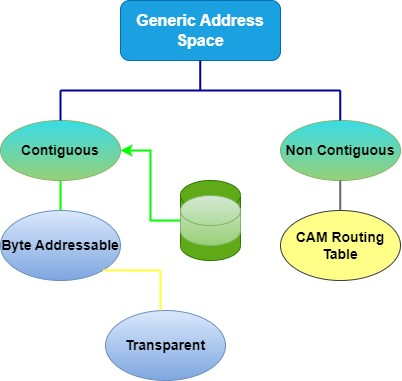

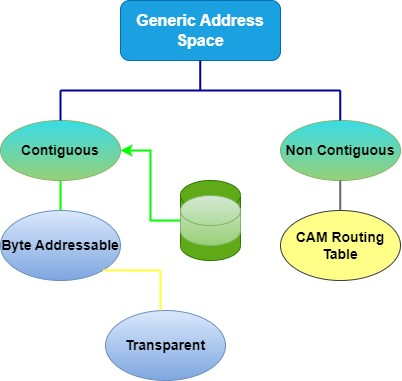

- PSS core library functions have base Address Space (addr_space_base_c), Traits (TRAIT), which are used to create a handle from an address space allocation claim, and also primitive functions that operate on a handle for reading from and writing to a contiguous byte-addressable space. This concept of Address space with Claims for Traits has been used to resolve the race condition during data transfer that arises in multi-threading systems with multiple CPU’s.

- This may be resolved by allocating an Address Space region (Contiguous) for Configuration Space Registers for either Type0 or Type1 Devices using Byte Addressability by PCIe End-point devices. The data can be written to these registers using generic operations. The allocate-able address space has unique addresses called atoms and is characterized by Traits.

- The memory modelling concept introduced - Address Space which is a uniquely addressable space of atoms. Fig. 1 and Fig. 2 explain the concepts of Address space, Regions and Atoms. A group of atoms in address space is called a region. Both address space and regions are characterized by their properties called traits and primitive functions over it. Regions are characterized by the same trait as its address space traits.

Fig:1 Address Space, Atoms, and Regions [3]

Fig:1 Address Space, Atoms, and Regions [3]

Fig:2 Classification of Address Space

Fig:2 Classification of Address Space

The Issue:

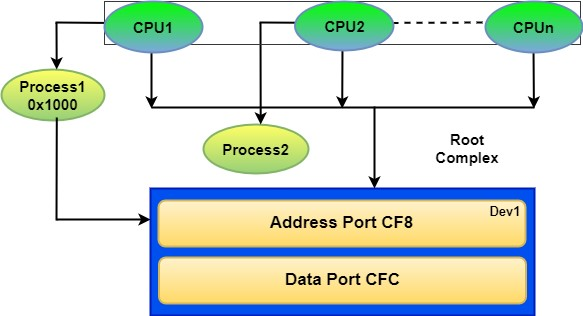

- PCIe enumeration is the process of detecting the devices connected to the PCIe bus. As part of PCIe enumeration, Switches and Endpoint devices are allocate memory from three PCIe slave address spaces of the HOST.

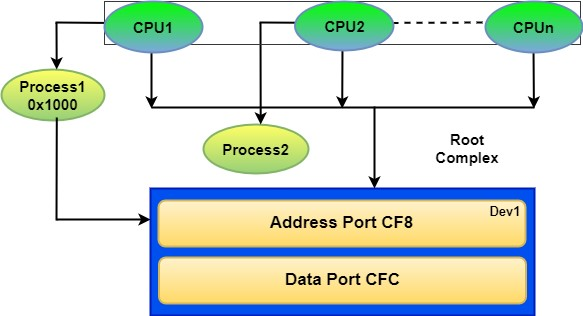

- A multi-threading system with multiple CPUs may cause a Race Condition during Data Transfer. Consider an example, as shown in Fig: 3, many CPUs want to write to PCIe end end point’s RxIn. Suppose CPU1 initiate a transaction on Address Port CF8 data is to be written to Data Port CFC. In the interim, another CPU2 may write on Address Port CF8 before the CPU1 has been able to write to Data Port. It will lead to a race condition.

Fig:3 Race Condition during Enumeration Process in PCIe

Fig:3 Race Condition during Enumeration Process in PCIe

Using Resource Share and Lock to avoid Race Condition

- The simple implementation requires the Ports to be declared as Resources and Lock and Share as the needs are for CPU to write/read.

- Using Traits to avoid conflict Data Integrity and Security and application of PSS2.0 Memory Modelling in PCIe

- Allocation of Address Space region (Contiguous Byte Addressable) for TYPE0 or TYPE1 Configuration space is achieved using Byte Addressability by PCIe End Point devices during Enumeration.

- The allocatable address spaces have unique addresses called atoms and are characterize by Traits. PCIe devices shall claim this Configuration Space region when it wishes to operate on it. Allocation trait is used by a PSS tool to define regions as well as match allocation claims. An allocation claim uses a trait to map to Configuration Spaces from address space. Configuration Space with traits that satisfy the claim’s trait constraints is the candidate for matching regions. The data can be written to these registers using the generic operations through address handles.

- Use the handle "src_handle" or "dst_handle" to check if write to ADDR PORT has been initiated already by having handle from claim written on the Address Port at Address Port CF8. Or use a temporary variable to record handle and check against that, so if a different CPU attempts to write to the Address Port before the first CPU having written to the Data Port at CFC, it will not be able to since the make handle value will be different.

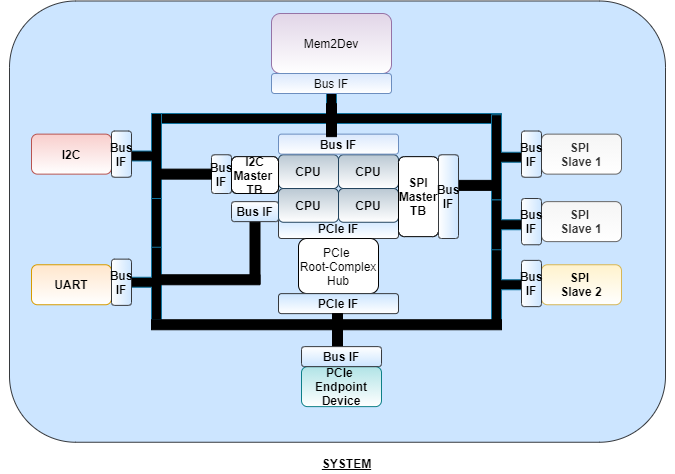

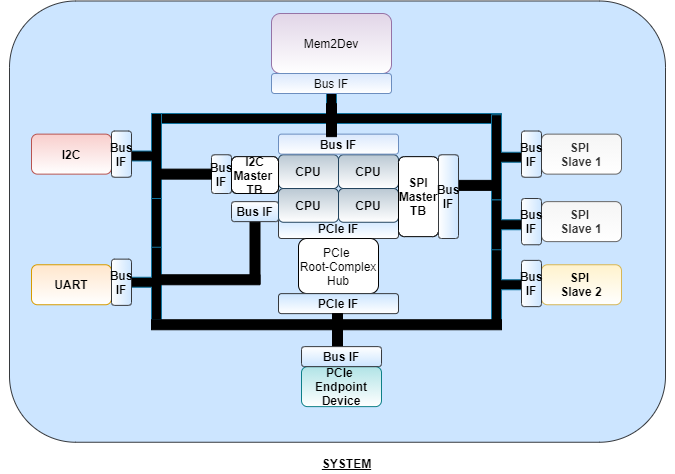

- The proposed concept can be extended to SOC environment using a Fabric Switch.

- The subject matter described here in subject to copyrights and patentable ideas and it is recommend that you click here to contact Silicon Interfaces for more information and an NDA for “PCIe Race Condition resolution with Data Integrity/Security using Memory Manager and Fabric Matrix"